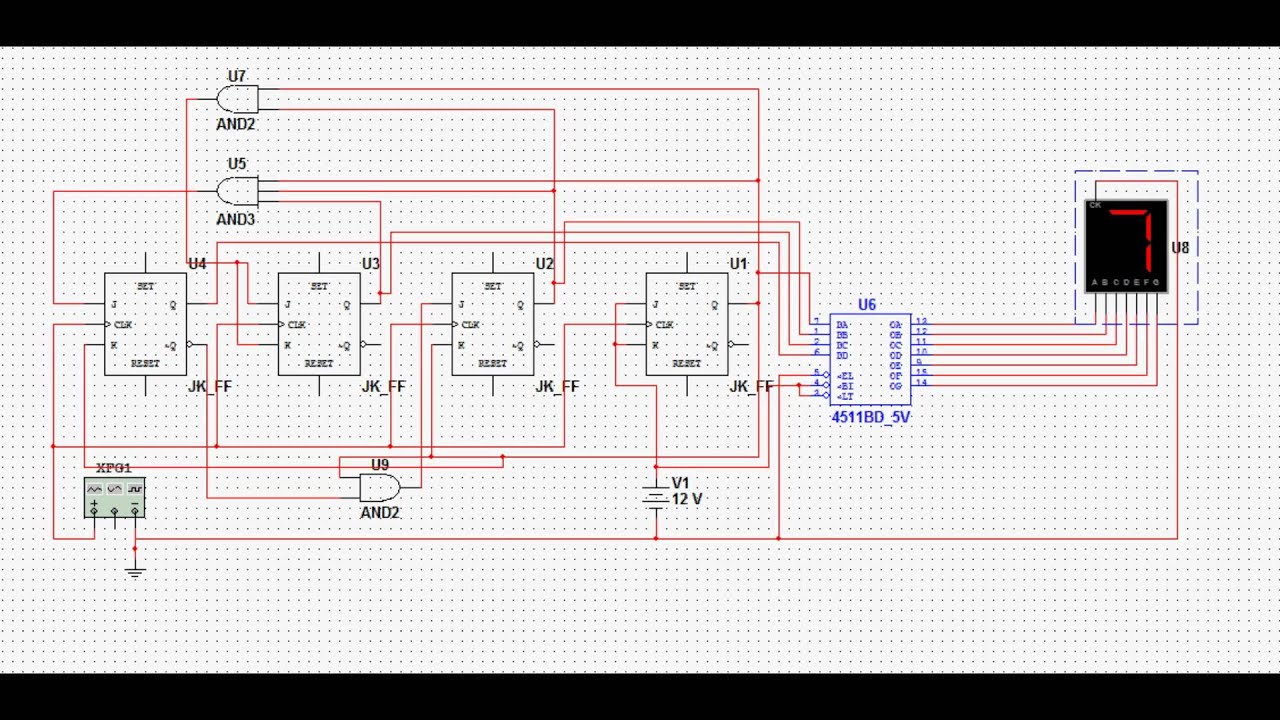

When CLK=4, the output of the counter is 011. When CLK=3, the output of the counter is 111. When CLK=2, the output of the counter is 110. The input D is just before the rising edge of the clock (CLK), denoted as Q0. The counter counts the state of cycles in a continuous closed loop. It contains 3 flip-flops, Q0, Q1, Q2 are the outputs of the flip-flops.

The clock signal(CLK) is used to know the changes in the output. The output of the proceeding flip-flop is connected as the input of the next flip-flop. Truth TableĬonsider the truth table of the 3-bit Johnson counter. 2-stage acts as a quadrature oscillator or generator that produces individual output signals of 90 degrees each concerning the input signal. 5-stage Johnson counter is used as a synchronous decade counter (CD4017) or divider circuit. For example, a 3-stage johnson counter can be used as a 3-phase and 120 degrees phase shift square wave generator. Standard 2,3 and 4 stages johnson counters are used to divide the frequency of clock signals with the help of varying feedback connections. So, the flip-flops can be enabled by clicking the Reset switch.ĬLK pin is used to observe the changes in the output of the flip-flops. It has preset and clear pins to initialize or start and reset the counted. Unlike the Master-Slave design, which needs a complete pulse, you can also build an edge-triggered design that triggers from a rising edge ↑ or a falling edge ↓.Consider the 4-bit Johnson counter, it contains 4 D flip-flops, which is called 4-bit Johnson counter. That’s why this configuration is called pulse-triggered JK Flip-Flop. So this circuit requires a complete pulse (0→1 →0) in order to change the output. Once the clock signal produces a falling edge ↓, a change from 1 to 0 (1→0), it triggers the slave section, causing the Q output to reflect the master’s output value. These signals are connected to the slave section, but this doesn’t trigger on the rising edge because the clock has been inverted. As a result, the value of the outputs in this section changes. As soon as the clock makes a rising edge ↑, which is a change from 0 to 1 (0→1), it triggers the master section.

0 kommentar(er)

0 kommentar(er)